知识点:

基本电路功能 与、或、非 异或 与非 或非

例如:“与非”门中的某一个输入值为“0”,那么它的输出值?

第一章

计算机系统:软件+硬件 软件: 系统软件、应用软件

摩尔定律P3

系统性能指标:P5 字长、MIPS

字长决定运算的范围和精度

运算器的组成,最重要的部件?P7

存储程序控制原理:提出者冯诺依曼,内容略 P10 冯诺依曼结构和哈佛结构

计算机系统的层次结构 高级语言级、汇编语言级、操作系统级、一般机器级、微程序设计级

第二章

10进制转二进制数 除2取余的方法 (权值 64、32、16、8、4、2、1)

原码、反码、补码、移码的计算方法

补码表示中,零的表示形式是唯一的

补码的真值公式 P21 公式2.9

计算某个数大于或小于某个值的条件(每一位的取值 参见课后题2)

移码主要用于表示浮点数中的阶码

P22 移码为补码变符号位

补码的表示范围:n位二进制补码所能表示的十进制整数范围是-2n-1~2n-1-1。

8位 -128~127

IEEE754 浮点数构成, IEEE754 会计算 BCD码 4位 ASCII码 7位

奇偶校验(含校验码的个数) 110101 数 P25 奇校验 奇数个1 110101 1 偶校验 偶数个1 110101 0 海明码特点,不要求计算 纠错

变形补码(双符号位)P29有计算题 判断溢出:

(1)双符号位 两个符号位异号,用异或门实现

(2)单符号位 最高位的进位和符号位进位异号,异或门来判定

运算器的主要功能:算术运算和逻辑运算

运算器虽有许多部件组成,但核心部件是算术逻辑运算单元

提高运算器高速性采用的措施:

先行进位 阵列乘除法 流水线

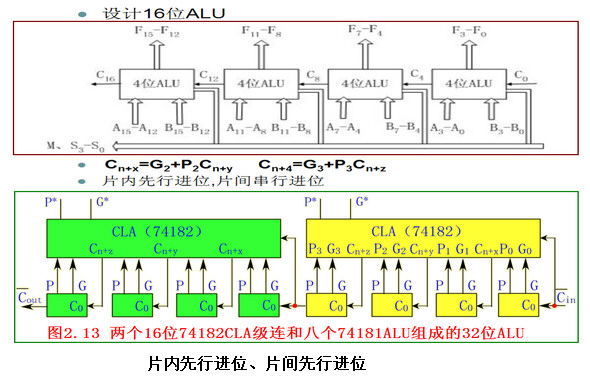

74181ALU 4位算术逻辑运算单元,支持16种逻辑运算、16种算术运算 组内先行进位

74182CLA 先行进位部件,可以实现多组74181ALU的组间先行进位 组合形式

字节编址

字编址: 给出容量、字长,计算寻址范围

例: 字长32位,存储容量64KB,

寻址范围 64KB/32=64K*8/32=16K,

第三章

存储器的层次

CPU能直接访问主存储器和cache 不能直接访问磁盘和光盘。 外存和内存比较 速度、容量、成本 半导体随机读写存储器

SRAM(cache)、DRAM(内存)比较

DRAM的两种刷新方式:集中式刷新、分散式刷新、异步刷新 P71 主存储器的性能指标:P65

存储容量、存取时间、存取(存储)周期和存储器带宽。 存取时间:发出读写命令到操作完成的实际时间。 存储周期:存储器进行连续读和写操作所允许的最短时间间隔

存储器扩展 P72 字长位数扩展,简称 位扩展 字存储容量扩展,简称 字扩展

一个512K×16的存储器,其地址线和数据线的条数

只读存储器和闪速存储器 EPROM 光擦可编程的只读存储器 E2PROM 电擦可编程的只读存储器

提高存储器访问速度的方法

双端口存储: 两套相互独立的读写电路 交叉存储:同时读写,顺序传送(流水) Cache:解决CPU和主存之间的速度匹配问题

计算Cache的命中率

主存与Cache的地址映射方式有三种:

全相联映射、直接映射、组相联映射 组相联映射(计算)P96 例8

Cache中常用的替换算法:最不经常使用(LFU)、

近期最不经常使用(LRU)、随机替换。

虚拟存储器:

采用虚拟存储器的主要目的是扩大存储器空间,并能进行自动管理 常用的虚拟存储器系统由哪两级存储器组成? 主存——辅存 P113 第24题

第四章

指令格式由操作码字段和地址码字段组成。

从操作数的物理位置来说,可将指令归结为三种类型:

存储器—存储器型,寄存器—寄存器型、 寄存器—存储器型 也可以写成(SS、RR、RS)

指令系统:

CISC:复杂指令集计算机 RISC:精简指令集计算机 特点:P131①②③ 简答

寻址方式 立即寻址——操作数在指令中 直接寻址——操作数在内存地址中 相对寻址——PC+偏移地址 间接寻址——操作数地址在内存地址中,

在内存中找到地址,根据地址再次访问内存

寄存器寻址——操作数在通用寄存器中 寄存器间接寻址——操作数地址在通用寄存器中,操作数在通用寄存器指定的内存地址中 X变址寄存器 D偏移地址

先变址再间址的寻址方式,有效地址 ((X)+D) 先间址再变址的寻址方式,有效地址 ((X))+D

程序控制类指令的功能是?转移指令 改变程序执行的顺序

汇编语言特性:硬件相关、编制难度大、执行速度快

设相对寻址的转移指令占两个字节,第一字节是操作码,第二字节是相对位移量(用补码表示),若CPU每当从存储器取出一个字节时,即自动完成(PC)+l->PC,设当前PC的内容为2009H,要求转移到2000H地址,则该转移指令第二字节的内容应为______。 解: 00H-09H-2H=F5H 当前PC 2009H,读指令2字节,变成200BH,要跳转到2000H,

需要跳转-BH,八位补码F5H

第五章

CPU寄存器,各寄存器的作用

程序计数器(PC) 指令寄存器(IR) 地址寄存器(AR)

状态条件寄存器(PSW) 通用寄存器

数据缓冲寄存器(DR) 操作控制器p142

作用:根据指令操作码和时序信号产生各种操作控制信号

分类:

硬布线控制器(公式Cn=?)P166 (简答) 微程序控制器

比较:速度快慢,修改难易

指令周期是指CPU从主存取出一条指令加上执行这条指令的时间

水平型微指令与垂直型微指令比较 P163-P164 水平性微指令一次可完成多个微操作,垂直型一次只能完成1到2个微操作 水平微指令

微命令的编码方式

微地址形成方式(填空)

并发性是指两个以上的事件在同一时间间隔内发生。P168

一个m段流水线处理器提高的效率 计算:第一条指令m,其他指令1,若有n条指令则m+(n-1),效率mn/[m+n-1] 若n很大,则mn/[m+n-1]约等于mn/n,即m

流水线的时钟周期由最慢的部件决定,例如部件执行时间为10ns、20ns、25ns,则为25ns

第六章

系统总线分类:P188 系统总线分为如下三组线:地址线、数据线、控制线

地址线的功能是:指定主存和I/O设备接口电路的地址

控制线的功能是提供主存、I/O接口设备的控制信号和响应信号及时序信号 数据线的功能是传输指令、数据、中断向量

计算总线带宽

总线仲裁方式:P194 集中仲裁:

链式查询 低优先级设备难得到响应 对电路故障最敏感 计数器定时查询 若从零开始,低优先级设备难得到响应 独立请求 响应最快

分散仲裁

从信息流的传送效率来看,单总线系统工作效率最低。

同步通信比异步通信具有较高的传输频率的原因:P197

用一个公共的时钟信号(统一时序信号)进行同步

常见的总线标准:ISA、EISA、PCI、PCI-Express

第七章

磁盘存储器:

平均存取时间:寻道时间、等待时间、数据传送时间 平均等待时间:转一圈时间的一半 磁盘驱动器向盘片磁层记录数据时,

采用的写入方式是串行的还是并行的?

第八章

I/O控制方式 P237

1程序查询方式 2中断方式 3 DMA方式 4通道方式

通道是一个特殊功能的处理器,它有自己的程序专门负责数据输入输出的传输控制

12程序方式实现,34硬件实现

中断中需要说明的问题:P241 尽管中断请求随机,只有在公操作时才处理中断请求 中断处理流程(选择题) 顺序排列

DMA控制器与CPU分时使用内存时,通常采用三种方法:

停止CPU访问、周期挪用、DMA和CPU交替访存。

采用DMA方式传送数据时,每传送一个数据要占用一个存储周期的时间。

计算

1、负整数原码表示,反码表示,补码表示和移码表示

(用8位二进制表示,并设最高位为符号位,真值为7位)。例如:-12 2、已知X=(1100)2,Y=(-1101)2,用变形补码计算X+Y、 X-Y,并指出是否溢出。 3、用带求补器的补码阵列乘法器计算X×Y。 P36例21

4、 下面的数使用IEEE754的32位浮点数格式,相等的十进制数是什么?

1 10000111 110 0000 0000 0000 0000 0000 - 128+4+2+1-127=8 1.11

-1.11*28

-111000000=十进制的?? 5.(补码的真值公式)

8位补码大于某数,则各位的取值 P21 公式2.9

简答

1. 提高存储器速度可采用哪些措施,请说出至少五种措施。

① 采用高速器件 ② 采用cache (高速缓冲存储器)

③ 采用多体交叉存储器 ④ 采用双端口存储器 ⑤加长存储器的字长 2. 请说明指令周期、机器周期、时钟周期之间的关系。(总结) 3. 简述机器指令和微指令之间的关系。 P161(总结) 4. RISC指令系统的三个重要特点是什么? P131

5. 硬连线控制器如何产生微命令?请问硬连线控制器输入信号来源主要有哪几个?

(P165-166)

6. 总线的同步通信方式与异步通信方式区别?适用场合? P197

区别点:数据传送操作„„、总线操作周期时间„„、设备之间沟通方式„„ 场合:设备速度差异„„ 应用题

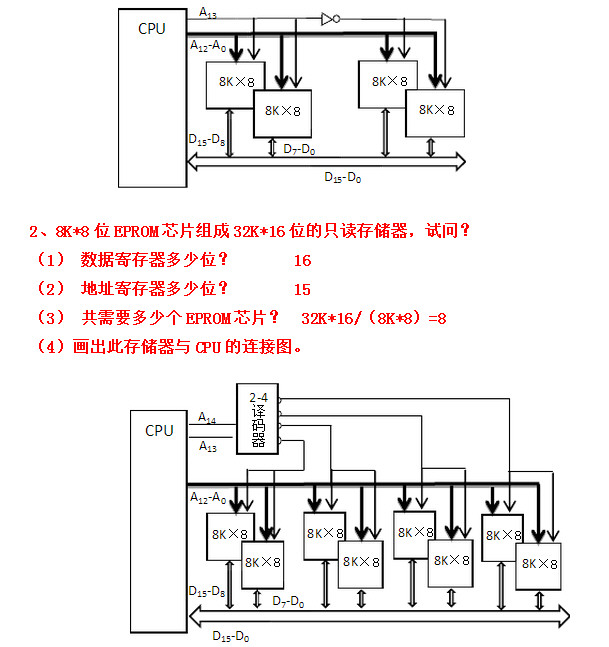

1、8K*8位EPROM芯片组成16K*16位的只读存储器,试问: (1) 数据寄存器多少位? 16 (2) 地址寄存器多少位? 14

(3) 共需要多少个EPROM芯片? 16K*16/(8K*8)=4 (4)画出此存储器与CPU的连接图。

2、指令格式如下所示,OP为操作码字段,试分析指令格式特点。

(1)单字长还是双字长,单地址还是多地址 (2)OP操作码字段最多指定多少种操作 (3)寻址方式、

RS、SS、RR中的何种,寄存器个数,寻址方式个数

3. 一个组相联cache由128个行组成,每组8行。主存储器包含2K个块,每块256个字。请表示内存地址的格式。(P96 例8)

4、微命令的互斥和相容,P156

5、虚拟存储器,给出虚地址和页表,求实地址 P113、第24题

6.解释流水线中都有哪些主要问题,其中数据相关有哪几种,举一例说明。

7、流水线 画图+计算 P184 第13题

8。设某机器有5级中断:L0,L1,L2,L3,L4,其中断响应优先次序为:L0最高,L1次之,L4最低,现在要求将中断处理次序改为L2L4L0L4L3,试问: (1)将表中各级中断处理程序的各中断屏蔽值如何设置?

每级对应一位,该位为0表示允许中断,为1表示中断屏蔽

(2) 若这5级中断同时发出中断请求,按更改后的次序画出进入各级中断处理程序的过程示意图。